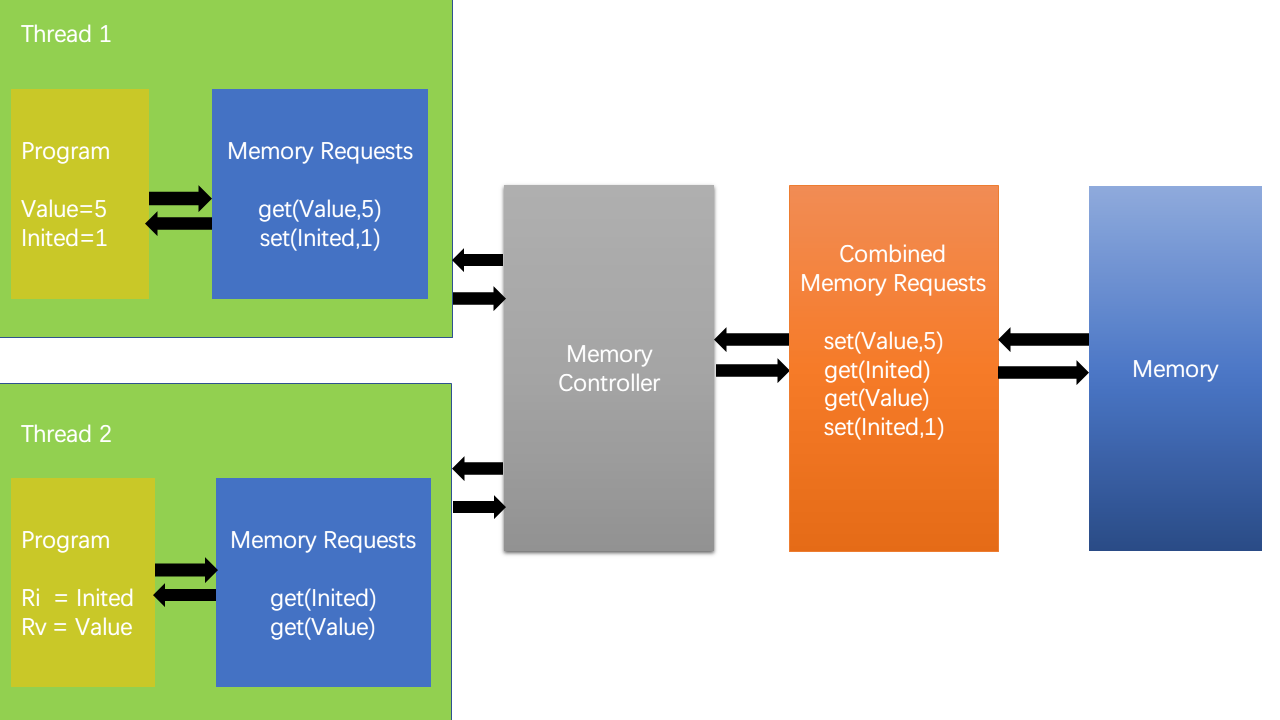

内存模型(Memory Model) 描述多线程交互时如何精确的访问内存数据状态

序列一致性内存模型

Sequential Consistency Memory Model

内存独立于任何使用它们的进程/线程

内存通过内存控制器连接到每个线程,内存控制器反馈每个线程的读写请求

单线程的读写请求会精确的按照线程的指定次序到达内存

也可能会和其他线程的读写请求按照一个未指定的方式交错进行

不可能会有当Ri=1(Value已被初始化了)时,Rv=0(Value未初始化)的情况发生

| req 1 | req 2 | req 3 | req 4 | Ri | Rv |

|---|---|---|---|---|---|

| value=5 | inited=1 | Ri=inited | Rv=value | 1 | 5 |

| value=5 | Ri=Inited | inited=1 | Rv=value | 0 | 5 |

| value=5 | Ri=Inited | Rv=value | inited=1 | 0 | 5 |

| Ri=inited | Rv=value | value=5 | inited=1 | 0 | 0 |

| Ri=inited | value=5 | Rv=value | inited=1 | 0 | 5 |

| Ri=inited | value=5 | inited=1 | Rv=value | 0 | 5 |

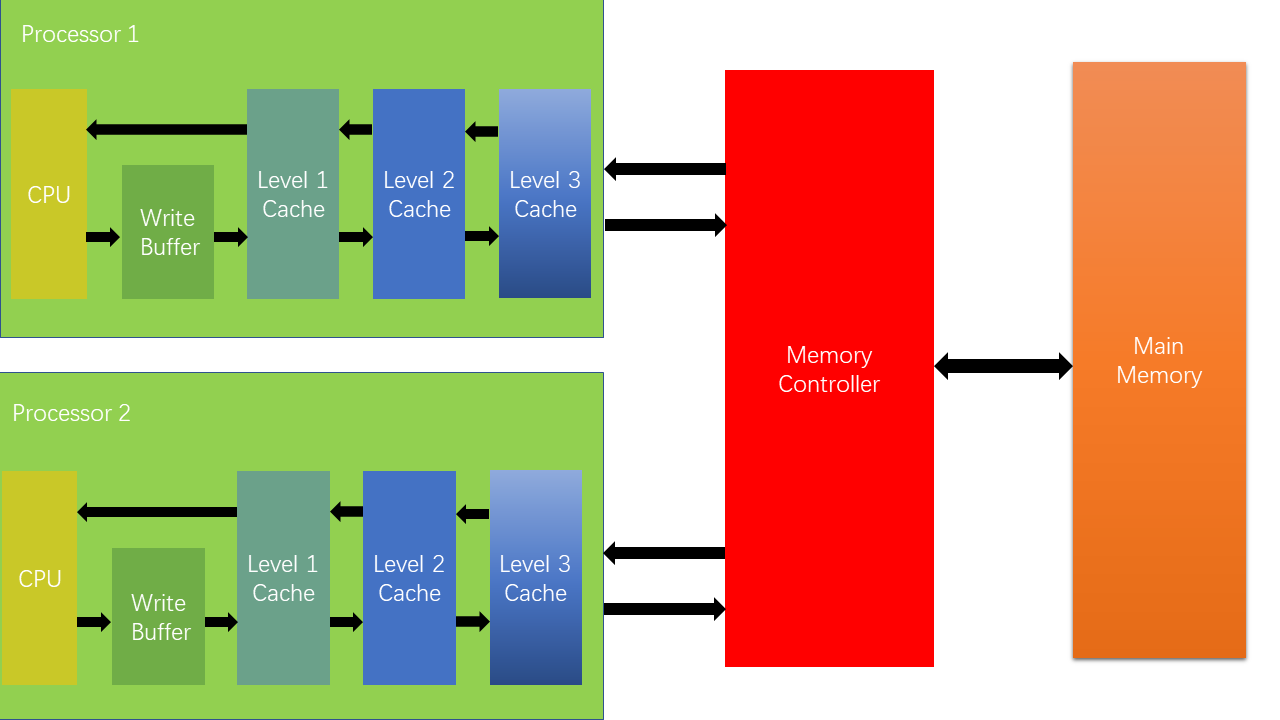

实际 多CPU机器的内存系统

cpu到内存的写操作有缓冲区,以便cpu可以在数据刷到以及缓存前可以继续下一个指令。最终数据会到达内存,这样数据就可以被其他处理器共享

不再会有单一内存视图

一个处理器缓存的一个内存位置的值,同时其他处理器也缓存了相同内存位置的数据,但是这个数据可能是过期的老的数据。这就可能导致处理器的缓存内容不一致。